异构IC封装:优化性能和成本

领先的集成电路(IC)铸造厂已经开始出货7纳米和5纳米晶圆,3纳米产品认证正在进行中。晶圆成本持续飙升,因为高晶体管密度需要更昂贵的工艺来制造它们。即使随着新节点的出现,缺陷密度可以保持相对平稳,单位面积的硅成本也会呈非线性增长。这些经济学已经把新的包装技术直接放到了未来产品架构的讨论中。

性能是最重要的,由新的硅节点提供的晶体管密度和时钟速度正在考虑功能应用。这是如何影响一个典型的高性能模具的其他领域,不需要在最新的硅节点上提高性能?

异构包装一直是业界追寻的答案,长期以来就犹如圣杯般的存在,但直到最近才作为设计方法用于实际生产。原本是单晶片的片上系统(SoC)的一部分从同质设计中分离出来,并在更小的独立硅晶片中创建。第一个趋势是删除与存储器和长距离串行/解串器(SerDes)类型通信的输入/输出I/O块。

这就形成了电气,功能,物理构件格局,使IC功能块可以反复认证和重复使用。就在几年前,以这种方式将原始投资分散到大量终端设备上是几乎想都不敢想的事情。

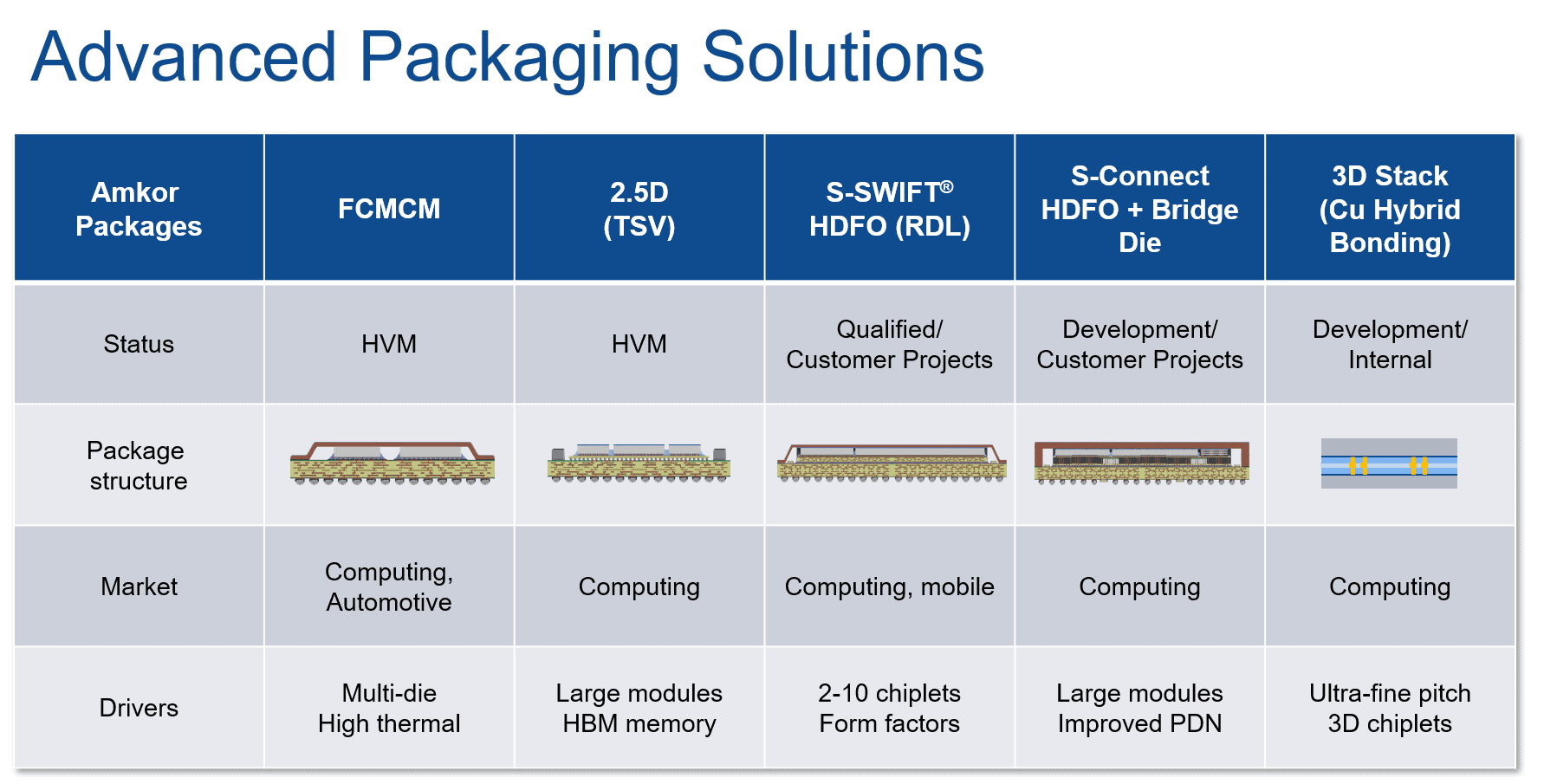

这一最新行业发展始于2.5d硅通孔(TSV)产品,该产品允许在同一个IC封装的应用程序特定集成电路(ASIC)中实现非常高密度的DRAM存储器或高带宽存储器(HBM)。作为功能块,这些电路项目目前正在从SoC中移除。仅举几例,示例包括作为独立硅小芯片的中央处理单元(CPU),以及GPU,通用计算和高速IO块。

为了推出这些产品,已经开发了几项关键技术,用于将几个或较多晶片集成到高性能离散晶片集合中,无论是逻辑晶片还是内存晶片,或者其他晶片。这些发展包括利用传统封装印刷电路板的高密度多晶片产品,所谓的多芯片模块(MCM)倒装芯片球栅阵列(FCBGA),以及非常精细的线路结构,例如2.5d TSV和hdfo产品。使用印刷电路板斯威夫特(s-swift)技术的新小芯片集成现已获得认证。S-SWIFT HDFO解决方案允许微线布线低至2-µm线和2-µm空间和6层结构。该模块制造技术已在过去3年中开发并升级,以实际允许小芯片和HBM存储器的集成。S-Connect是一种结合了HDFO和桥接的产品,处于内部认证阶段。

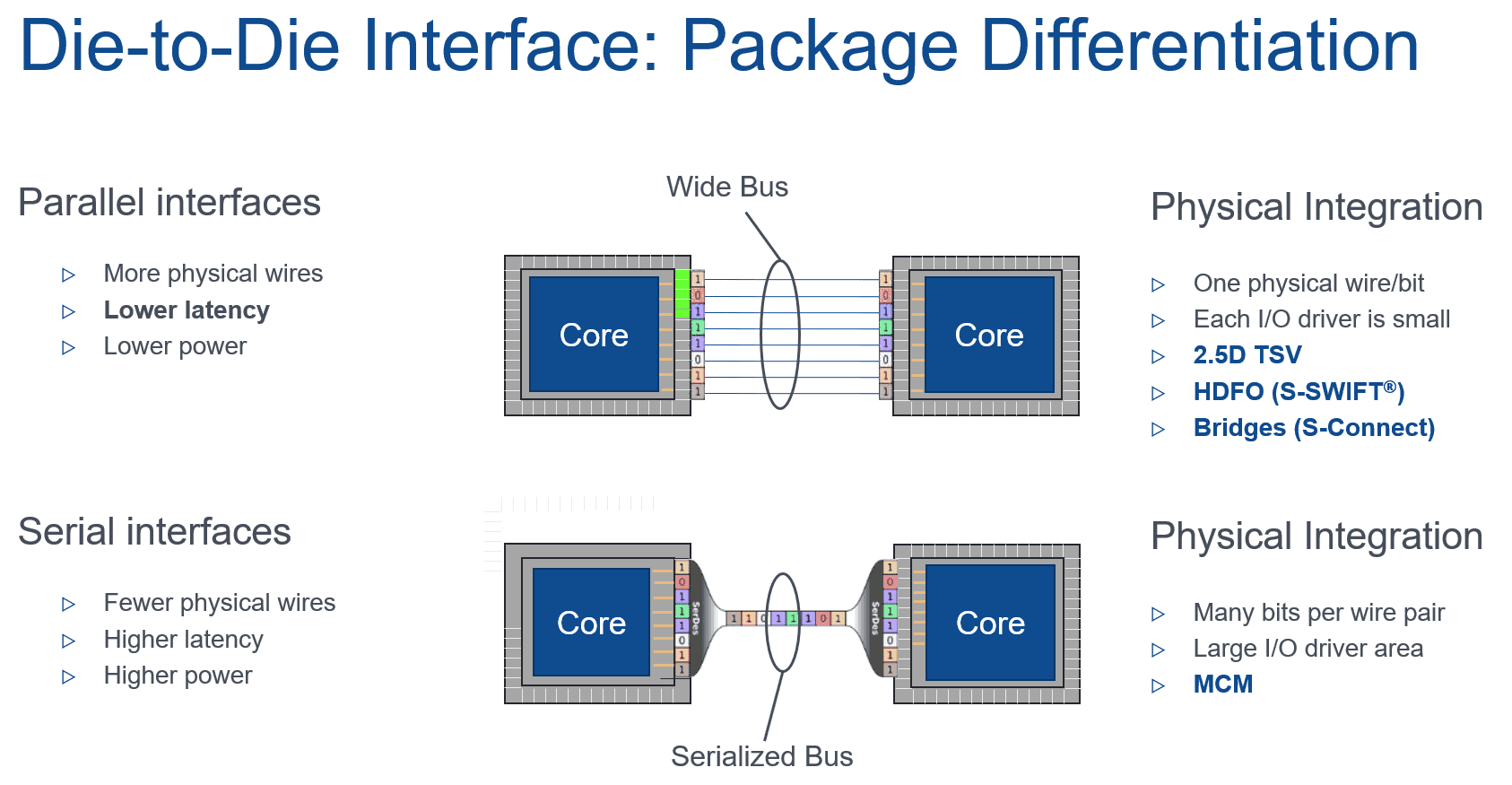

使用小芯片实现异构结构的IC封装技术的选择很大程度上受小芯片之间通信接口的影响,参见图 1。对于许多应用来说,晶片之间具有100或1000 IO的高速并行接口是首选,而这需要高密度互连,例如使用硅介质层或HDFO S-SWIFT或桥接技术(S-Connect)的2.5 d TSV。

图 1:晶片间接口选择

swift利用铜微线光刻和有机介电质来实现高水平的信号路由密度,在现场制造。S-Connect更谨慎地使用相同的高密度RDL技术,但增加了高密度桥以帮助小芯片之间的极高密度布线。未来还使用铜混合键合提供的超密集垂直晶片间互连的3d晶片堆叠补充2d集成。

这些包装技术的未来是光明的。仅在去年,用于小芯片2d集成的新产品设计增加了4倍。随着公司持续在异构IC封装路线中取得进展,提高硅架构灵活性,小芯片重用,缩短上市时间和降低总体成本持续推动封装行业做出这种创新。

关于作者

迈克·凯利是Amkor科技狗万注册地址的高级封装和技术集成副总裁。凯利于2005年加入公司,领导了EMI屏蔽,热增强型封装,传感器和高密度MCM封装(包括2.5 d TSV封装和HDFO)的封装开发。他从事电子与IC封装设计和制造25年,管理的项目包括聚酯柔性电路,共晶倒装芯片,IC封装设计和信号完整性等。凯利在该领域拥有40多项专利,并拥有机械和化学工程的硕士学位。