以电气方式连接多晶粒的封装技术

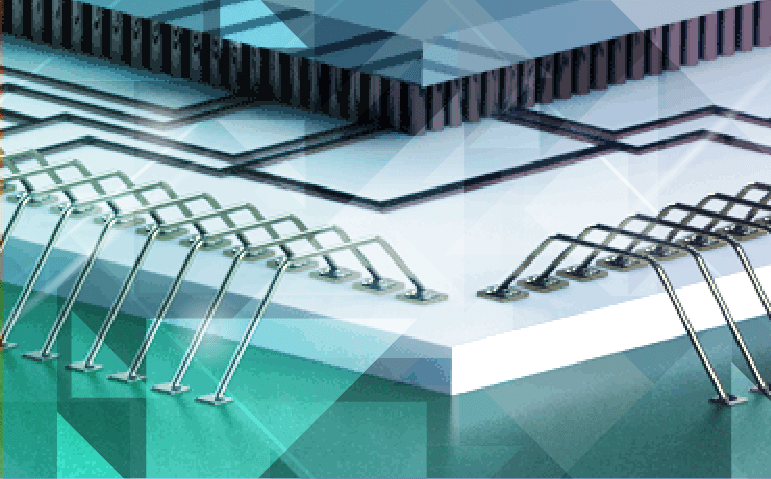

公司积极,有策略地推进芯片内建芯片(CoC)的研究和开发。CoC (DSBGA / DSMBGA)的设计无需硅通孔(TSV)而以电气方式连接多晶片。小微于100米的面对面小间距倒装芯片互连实现了电气互连。母晶片通过倒装芯片凸块或焊线与封装相连,一般以粗间距与封装匹配。两个(或更多)晶片能以更快的速度更高效地传输,采用更高频率带宽,并减小电阻(R),电感(L)和电容电阻,而成本比TSV更低。

公司通过微传感器、汽车微控制器,无线,光电和移动领域各种应用中的CoC技术为大量产品提供支持。

有问题?

点击下方的“获取信息”按钮,

联系公司专业人士。