Dsmbga의열시뮬레이션및라지바디hdfo의열-기계결합시뮬레이션

장치수가늘어나고,전력밀도가높아지고,이기종통합이점점보편화되면서전자패키징은점점복잡해지고있습니다。모바일공간에서인쇄회로기판(PCB)위에개별구성요소로자리했던시스템들이이제는관련된모든수동장치및인터커넥트와함께하나의SiP(시스템인패키지)로구현되고있습니다。고성능컴퓨팅와데이터센터패키지에서도비슷한추세가나타났습니다。메모리가단일,터포저기반통합패키지로통합된것입니다。현대식첨단패키지가급속도로발전하면서나날이복잡해지는것과달리,기계적스트레스와열전달에관한물리적법칙은여전히존재합니다。최근몇년동안패키지소재개발이활발해지고있지만,기계적스트레스와열문제를해결할혁신적인소재는아직없습니다。

패키지설계과정에서엔지니어링의사결정의방향을잡으려면장치성능을예측하고,장치오류를연구하고,근본원인을탐구하고,최적화연구를수행하는기계적(구조적및열적)시뮬레이션을활용하는것이적절합니다。이번글에서는시뮬레이션충실도가높아야하는복잡한패키지에만존재하는난관을집중적으로알아보고,시뮬레이션을활용해패키지열성능을특성화한두가지사례를살펴봅니다。

사례연구1:모바일시장패키징

첫번째사례연구는시스템产品部패키지(SiP)장치가모바일시장에적용된사례입니다。이패키지는적층형인쇄회로기판(PCB)두개사이에샌드위치처럼놓이게되며,이경우방열이제한됩니다。열은PCB로반드시전달되어야하고,패키지총두께가제한되어상단구리히트스프레더를사용할수없습니다。

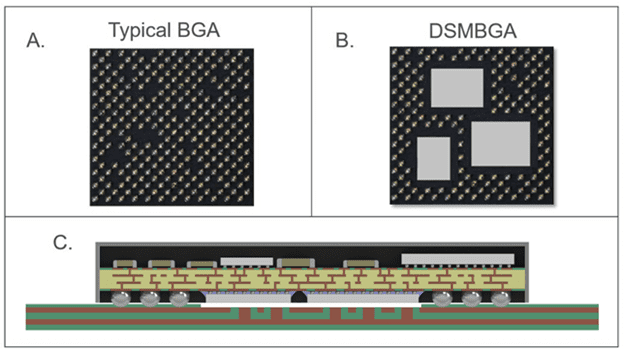

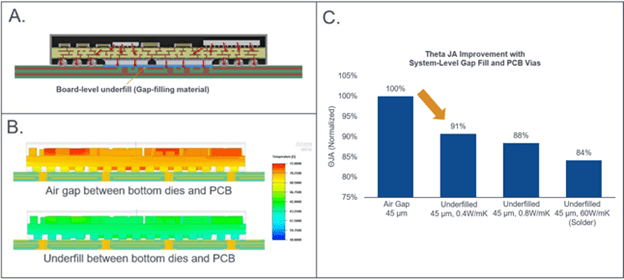

양면몰드볼그리드어레이(DSMBGA)에서시험한개선사항으로고열전도에폭시몰딩화합물(EMC)대형구리포스트로의BGA교체,밑면이노출된다이와PCB사이의틈을메우는시스템레벨언더필을시험해보았습니다(그림1)。이옵션들중에서시스템레벨언더필만이상당한수준의열개선을이뤘습니다。표준电平대기상태에서접합부에서주변부(ΘJA)까지의열저항이약10%감소한것입니다。구리포스트개선은미미한수준이었고,고열전도EMC는개선정도가도1%되지않았습니다(그림2)。이시뮬레이션은西门子Simcenter Flotherm과함께진행했습니다。

그림1:일반BGA (A)와기판밑면에컴포넌트와다이가부착된DSMBGA (B)의BGA레이아웃차이。Dsbga단면도(c)

그림2:(a)기판밑면에부착된다이아래에있는보드레벨언더필위치。(B)언더필이없는패키지(위)와언더필이있는패키지(아래)의온도차이시뮬레이션。이미지들의색상스케일은일정합니다。(c)다양한언더필열전도율에대한시뮬레이션결과도

사례연구2:라지바디패키지

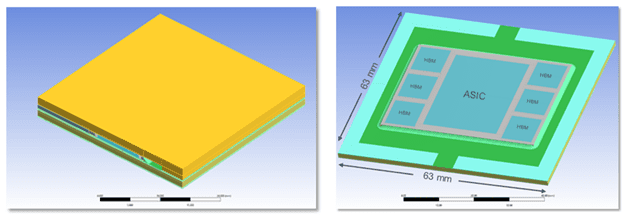

두번째로살펴볼사례연구는중앙주문형집적회로(asic)및다중고대역폭메모리(hbm)모듈이탑재된라지바디(고밀도팬아웃)패키지의구조——열결합시뮬레이션입니다(그림3)。열시뮬레이션은대부분(속도와단순성을위해)ASIC / HBM모듈상단과덮개하단사이의열인터페이스재료(TIM)접착층두께가일정하다고가정합니다。이연구에서는ASIC및모듈영역에서(뒤틀림으로인한)접착층두께의변화가패키지의열성능에어떻게영향을미칠수있는지더잘이해해야했습니다。

그림3:라지바디hdfo모델분기대칭도(왼쪽)。Asic +6 HBM hdfo모듈을明文시하기위해리드를숨긴확장뷰(오른쪽)

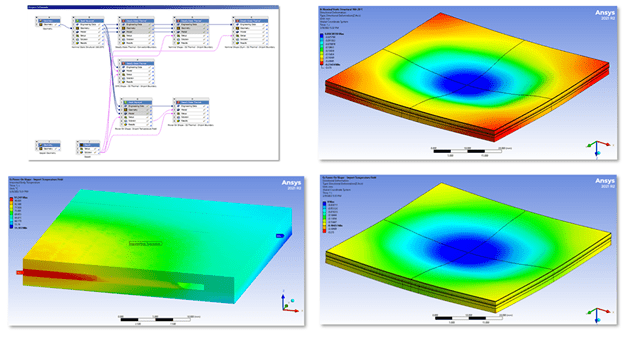

63 x 63毫米HDFO패키지는앤시스워크벤치메커니컬구조에적용할수있는'출력'온도프로파일을생성하기위해앤시스아이스팩에서먼저시뮬레이션했습니다。이온도프로파일에는두가지목적이있습니다。첫번째는스트레스를생성하고재료별열팽창계수차이로인한모델의변형을계산하기위해구조모델전반에온도조건으로적용하는것입니다。그리고두번째는,변형된기하학적구조와다양한蒂姆접합층의앤시스메커니컬정상상태열시뮬레이션에적용할리드-상부및기판-하부온도경계조건을계산하는것입니다(그림4)。

그림4:(왼쪽상단부터시계방향)앤시스프로젝트스키메틱,열및구조모델을결합하면서연결된하위시스템패키지뒤틀림,20°C,데드버그보기(기판바닥에서보기)。'출력'열경사도가적용된데드버그보기(20°c뒤틀림과동일한색상스케일)。아이스팩에서추출된온도프로파일경계조건

그림4:(왼쪽상단부터시계방향)앤시스프로젝트스키메틱,열및구조모델을결합하면서연결된하위시스템패키지뒤틀림,20°C,데드버그보기(기판바닥에서보기)。'출력'열경사도가적용된데드버그보기(20°c뒤틀림과동일한색상스케일)。아이스팩에서추출된온도프로파일경계조건

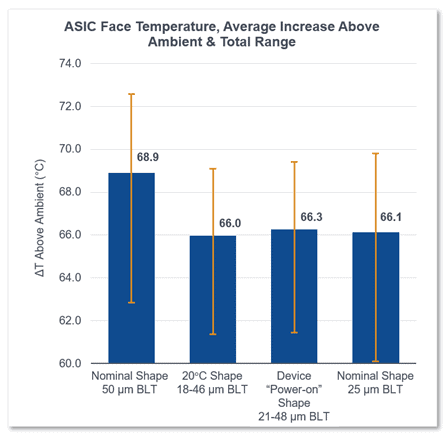

그런다음변형된형상(실온변형기준선의경우20°C및아이스팩시뮬레이션”출력'온도에서계산)을열모델의형상으로사용했습니다。변형되지않은기준선을기준으로측정된활성표면접합온도의변화를다이표면전체에걸쳐계산하고출력했습니다(그림5)。

그림5:다양하게시뮬레이션된asic온도의온도결과차트。오차막대는다이면전체의총온도범위를나타냅니다

결론

앤시스기계적열모델은다이면전체에서ASIC평균온도88.9°C이고최고92.6°,최저82.8°C(다이전체의온도델타9.7°C)를보여줍니다。20°C모양모델은다이온도평균86.0°C,최고89.1°C,최저81.4°C(다이전체의온도델타7.7°C)를보여줍니다。“출력'형태모델은평균다이온도86.3°C,최고89.4°C,최저81.4°C(다이전체의온도델타8.0°C)를보여줍니다。

접착층두께(BLT)변화를담당하는모델의다이온도는,접착층이모듈중앙보다얇은곳도있고두꺼운곳도있어결과적으로일관성을가집니다(다이전체에걸쳐더낮은델타)(50µm BLT기준선기준)。이사례연구를통해향후모델의불확실성을더잘이해할수있습니다。

작성자정보

内森惠는앰코에서패키징및기계적시뮬레이션을담당하는수석엔지니어입니다。전자패키징분야의업무를다루기전에는차량탑재컴퓨터랙인클로저,무선열설계,데이터센터열분석및시스템통합등의프로젝트에참여했습니다。그는시스템레벨에서의컨텍스트와패키지수준에서의기계적시뮬레이션에대한이해를제공합니다。Witchurch는서던캘리포니아대학교에서기계공학학사학위를받았습니다。