半導体ストーリー:パッケージ材料とコストダウンVol1

半導体とコスト削減

公司在故事読者の皆さん,こんにちは。2月も終盤になり,もうすぐ3月ですね。暖かい春が待ち遠しいです。厳しい冬と早くお別れしたいものです。つい先日,私は大型ショッピングセンターの家電コーナーをのぞいて見ました。そこで私は,大型の超高解像度テレビ(UHD)に心を奪われてしまいました。カラフルなシーンが薄型のワイドスクリーンいっぱいに広がり,しばらくうっとりしていました。更に予想より安かったので,購入したい気持ちに抗うのが大変でした。ほんの数年前に比べれば,この最新モデルはパフォーマンスも良くなり,画面も大きくなりましたが,価格はほぼそのままか,安くさえなったものもあります。

高校時代,友人の一人が父親から内緒で拝借した携帯電話を見せてくれました。2000年私は,それがドルもすると知って驚きました。通話機能のみの携帯でしたが,そのサイズはレンガよりも大きいものでした。昨今,携帯電話は最先端の機能を備え小型化されましたが,不思議なことに価格は下がり続けています。これはなぜでしょう。多くの答えがあると思いますが,私の考えでは,技術の進歩と,最近よく言われる生産コストの削減がその理由だと思います。フラットパネルテレビに使用されている半導体パッケージは価格面で競争力を出すために多くのコスト削減ステップを経たに違いありません。この値段は,半導体パッケージングに注がれた努力の結果なのでしょう。たくさんお話したいことがあるのですが,今日は材料のストーリーを扱います。

半導体と金ワイヤ

まず,半導体パッケージに使用される材料を見てみます。パッケージには複数の材料が必要です。リードフレームまたはプリント基板(PCB)のような基板があり、エポキシモールド樹脂(EMC)、チップ接着剤、金ワイヤ、まだまだあります。材料を製造する企業は競争力のある価格を出すために多大な努力をします。それでは、パッケージングを行う企業はどのようにして材料コストの削減ができるのでしょうか。

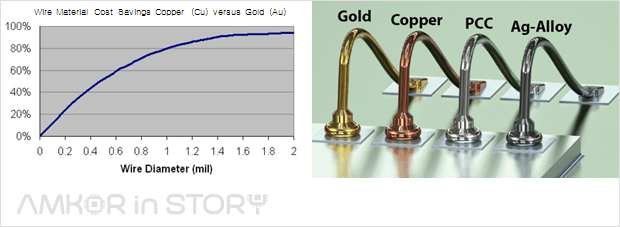

まず,金ワイヤがあります。これは電気的にチップを外部のI / O端子へ接続します。“金のような値段“という言葉をご存知でしょうか。文字通りです。高価なのです!金相場は過去30年にわたり安定的に上昇傾向にあります。半導体パッケージを製造する企業としては金の価格が上がるのに比例してパッケージのコストが上がっては困ります。できる限り金ワイヤを使用する量を減らしてコスト削減につなげたいものです。

人間の髪の毛の太さは通常50から100μmです。それに対し,パッケージに使用される金ワイヤははるかに細く,通常25μm未満です。より細いワイヤは,価格的により競争力があります。しかしながら,無条件に細くすることはできません。ワイヤが細くなるにつれ電気特性は悪化し,またモールド工程でワイヤ流れや揺れを起こしやすくなり,隣接するワイヤとショートを起こすことになります。

金は高価ですが,より安価な材料もあります。最も競争力のあるものは銅(铜)です。銅が金と同じくらい高価になることはあり得るでしょうか。実は銅は簡単に酸化してしまい,また金より硬いので,プロセスに注意を払う必要があり,銅を使用する総コストを増加させます。競争力のある材料は他にもたくさんあります。

材料を変更することとは別に,金ワイヤの使用量を減らすこともできます。できる限りチップの近くへワイヤを接続することで,これが可能になります。ワイヤに加えて,チップを基板に接着させるためには何らかの接着剤が必要です。この作業に使うのがエポキシですが,一部の液状エポキシはキュアの最中にチップの外側へ流出します。ワイヤがチップに近すぎる位置で接続され,エポキシがその上を覆った場合には,適切なボンディングができなくなる場合があります。エポキシではなくダイアタッチフィルム(DAF)を使用すればワイヤをかなり短縮することができます。また,配線の厚さと幅を減らしてもワイヤを短縮することができます。しかしながら,それらを減らすことは通常基板の作成コストが高くなることになりますので,これらの側面をすべて検討して設計しなければなりません。

半導体と基板

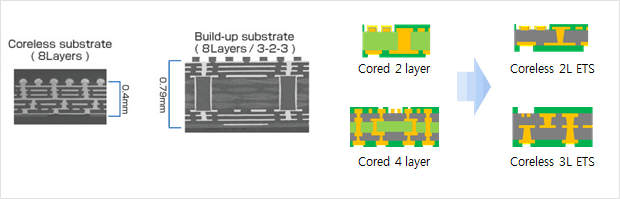

2番目にお話したいことは,基板のことです。最新のパッケージデザインの傾向の一つは,コアのない基板ーコアレス基板を使用することです。旧来の基板設計にはその両側に配線層のある太いコアが必要でした。コアがない場合,パッケージ全体の価格と厚さの両方が削減できます。そのためこの技術にはかなりの注目が集まっています。しかしながら,世の中にタダ(無料)のランチのようなものはありません。比較的硬いコアを持たないことから,反りに影響を与え,また電気特性に関して問題を起こす可能性もあります。そのため,さまざまな角度からパッケージのパフォーマンス評価を行う必要があります。

配線層を増やすことは製造プロセスにより多くの手間がかかることになり,コストが上昇します。配線層を減らすことは生産コストの削減に役立ちます。これを行う一つの方法はパターン埋込み型基板(ETS:嵌入式微量基质)と呼ばれるコアレス基板技術を用いる技術です。コアの代わりにプリプレグを用いることで配線層を減らすことができるため,近年注目を浴びています。

私は材料サプライヤーのオフィスでホワイトボードに”命がけで製造コストを削減しろ”と書かれているのを目にしたことがあります。少し驚きましたが,製造コストを節約することは単なる選択肢ではなく,競争力を維持し続ける唯一の方法だと改めて思ったのです。その言葉は,緊急性と覚悟を表現する言葉として認知されなければなりません。製造コストの削減が重く受け止められれば,製品の価格は下がり,家電メーカーは前述したUHDテレビのような家電製品により多くの機能を追加することができます。この言葉はもう一度私に製造コストの削減は現場において極めて重大な問題だと気づかせてくれました。今回私は材料について語りましたが,次回は製造プロセス中に使用される技術を検討してみます。次回にご期待ください。

作者Gyuik Jeong

大志を持って公司に入社してすでに10年になります。10年は地球の環境を変えるのに十分な時間だとも言われますが,私はすべての仕事に対して新人のように新鮮な興味や関心を持ち,仕事を楽しみ続けることを望んでいます。