独特的SWIFT功能包括:

- ポリマーベース絶縁層

- マルチチップ,大型チップ対応

- 大型パッケージボディ対応

- 接続密度2μmライン/スペースまで可能(SoCパーテショニングアプリケーションに貢献)

- 铜ピラーチップ接続:30μmピッチ対応

- スルーモールドビア(烟草花叶病毒®)または高さのある铜ピラーを利用した3 d /パッケージ・オン・パッケージ対応

- 电平MSL3 CLR / BLRに適合

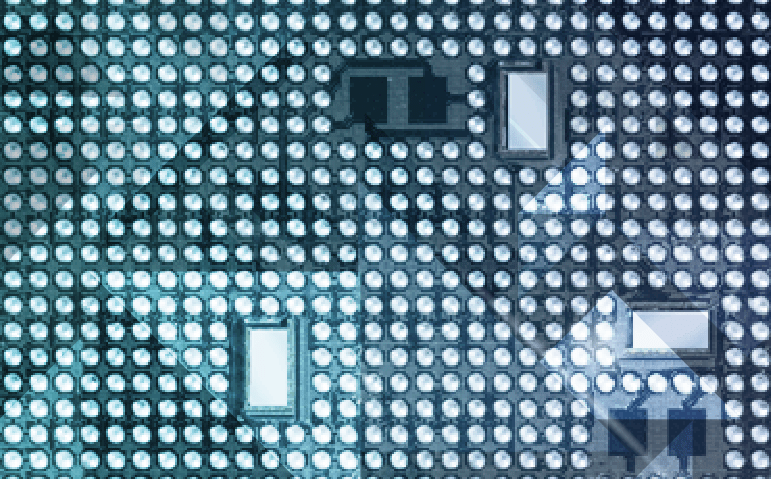

主要な組立技術により,この特色ある迅速パッケージの製造が可能となります。ステッパー装置を使用することで,2/2μmライン/スペースが実現でき,通常2.5 dのTSVが使用されるSoCパーティショニングおよびネットワーク機器に求められる高密度のチップ間接続が可能になります。ファインピッチチップのマイクロバンプは,アプリケーションプロセッサやベースバンド機器などの先端製品向けに高密度接続を提供します。さらに,高さのある铜ピラーが,斯威夫特の最上部に高度なメモリを実装するための高密度積層インターフェイスを可能にします。

ご質問やお問合せはこちらまで

以下の”リクエスト”をクリックしてご連絡ください